Barkatech Consulting, LLC | Home Page

- Details

- Written by Javed Barkatullah

- Category: About

- Goldstrike 1(TM): Cointerra’s First Generation Crypto-currency Mining Processor for Bitcoin: Javed Barkatullah, Timo Hanke, IEEE Micro, Issue 99, pp .

- Goldstrike 1(TM): Cointerra’s First Generation Crypto-currency Processor for Bitcoin Mining Machines : Javed Barkatullah, Timo Hanke, Ravi Iyengar, Ricky Lewelling, Jim O’Connor, Hot Chips Symposium HC26, Aug. 10-12, 2014.

- Skewed Repeater Bus: A Low-Power Scheme for On-Chip Buses: Maged Ghoneima, Muhammad Khellah, James Tschanz, Yibin Ye, Nasser Kurd, Javed Barkatullah, Yehea Ismail, Vivek De ; IEEE Transactions on Circuits & Systems, 2008, vol. 55, issue 7, pp 1904-1910.

- A Skewed Repeater Bus Architecture Technique for On Chip Energy Reduction in Microprocessors: Muhammad Khellah, Maged Ghoneima, James Tschanz, Yibin Ye, Nasser Kurd, Javed Barkatullah, Yehea Ismail, Vivek De ; ICCD 2005, pp 253-257.

- Reducing the Impact of Power Supply Noise on Microprocessor Performance: Tawfik Rahal-Arabi, Keng L. Wong, Javed Barkatullah, Matthew Ma, Greg Taylor, IEEE 14th Topical Meeting on Electrical Performance of Electronic Packaging 2005, pp 307-310.

- Enhancing microprocessor immunity to power supply noise with clock/data compensation: Tawfik Rahal-Arabi, Greg Taylor, Javed Barkatullah, Keng L. Wong, Matthew Ma, IEEE Symposium on VLSI Circuits, June 16-18 2005, pages 16-19.

- A Design for Digital, Dynamic Clock Deskew: Charles E. Dike, Nasser A. Kurd, Priyadarsan Patra, Javed Barkatullah, ; 2003 Symposium on VLSI Circuits, Digest of Technical Papers, pp 21-24.

- A Replica-biased 50% Duty Cycle PLL Architecture with 1x VCO: Nasser Kurd, Jed Griffin, Javed. Barkatullah, Ian Young; IEEE International Solid-State Circuits Conference, 2003. Digest of Technical Papers, 9-13 Feb. 2003, Pages:426 - 504 vol.1

- NWD 1XVCO Replica-Biased PLL: Nasser A. Kurd, Jed Griffin, Javed Barkatullah, Ian Young; DTTC 2003.

- A Digital Dynamic Mesh Deskew and Its Stability Criteria: Charles E. Dike, Nasser A. Kurd, Priyadarsan Patra, Javed Barkatullah, DTTC 2002

- Multi-GHz Clocking Scheme for Intel(R) Pentium(R) 4 microprocessor: Nasser Kurd, Javed Barkatullah, Rommel Dizon, Tom Fletcher, Paul Madland; IEEE International Solid-State Circuits Conference, 2001. Digest of Technical Papers, 5-7 Feb. 2001; Pages:404 – 405.

- Estimation of Clock Inaccuracy for High Speed Chip Design: Javed Barkatullah, Paul Madland; Proceedings Intel Design,Test & Technology Conference, pp. 285-289, July 1997.

- High-speed Digital Circuit Timing Race Modeling: Sammie Samaan, Milo Sprague, Javed Barkatullah; Proceedings Intel Design,Test & Technology Conference, pp. 291-296, July 1997.

- Management of Power Supply Noise Using Die, Package and Board Level Solutions: Tom Mozden, Javed Barkatullah, S. Rajgopal, D. Weiss; Intel Technology Journal, pp 49-61, Fall 1995.

- Domino Logic Design Using Cells: Tom Fletcher, Javed. Barkatullah, A. Dedhia; Proceedings Intel Design, Test and Technology Conference, pp 91-94, June 1993.

- A Transmission Line Simulator for High-speed Interconnects: Salim Chowdhury, Javed Barkatullah, D. Zhou, E. W. Bai, K. E. Lonngren; IEEE Transactions on Analog and Digital Signal Processing, Volume: 39 , Issue: 4 , April 1992; Pages:201 – 211

- Transient Analysis of Lossy Transmission Lines in Integrated Circuits: Javed Barkatullah, Salim Chowdhury; IEEE International Symposium on Circuits and Systems, 1992. Proceedings Volume: 5, 3-6 May 1992; Pages:2352 - 2355 vol.5.

- An Efficient Method for Computing Transient response of Integrated Circuits with Lossy Transmission Lines: Salim Chowdhury, Javed Barkatullah, ; Proceedings [3rd] European Conference on Design Automation, 1992, 16-19 March 199 ; Pages:219 – 223.

- A Transmission Line Simulator for GaAs Integrated Circuits: Javed Barkatullah, Salim Chowdhury; 28th ACM/IEEE Design Automation Conference, June 17-21, 1991; Pages:746 – 751

- Estimation of Maximum Currents in MOS IC Logic Circuits: Salim Chowdhury, Javed Barkatullah, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Volume: 9 , Issue: 6, June 1990; Pages:642 – 654.

- Current Estimation in MOS IC Logic Circuits: Salim Chowdhury, Javed Barkatullah.; IEEE International Conference on Computer-Aided Design, 1988. ICCAD-88. Digest of Technical Papers, 7-10 Nov. 1988; Pages:212 - 215

- Details

- Written by Javed Barkatullah

- Category: About

- Apparatus for power consumption reduction, Patent Number: US 7562316

- Frequency management apparatus, systems, and methods, Patent Number: US 7282966

- Clock modulation circuits with time averaging, Patent Number: US 20070238434

- PLL with controlled VCO bias, Patent Number: US 20070046343

- Method and apparatus for power consumption reduction, Patent Number: US 20060259890

- Method for power consumption reduction, Patent Number: US 7096433

- Frequency management apparatus, systems, and methods, Patent Number: US 20060066376

- Adaptive body bias for clock skew compensation, Patent Number: US 7015741

- Adaptive frequency clock generation system, Patent Number: US 20050218955

- Method and apparatus for detecting on-die voltage variations, Patent Number: US 20050184764

- Method and apparatus for optimizing clock distribution to reduce the effect of power supply noise, Patent Number: US 6934872

- Adaptive body bias for clock skew compensation, Patent Number: US 20050134361

- Method and apparatus for power consumption reduction, Patent Number: US 20050102642

- Digital clock skew detection and phase alignment, Patent Number: US 6622255

- Method and apparatus for optimizing clock distribution to reduce the effect of power supply noise, Patent Number: US 20030115493

- Method and apparatus for synchronizing clock signals in a multiple die circuit including a stop clock feature, Patent Number: US 5706485

- Method and apparatus for optimizing clock distribution to reduce the effect of power supply noise, Patent Number: US 693487

- Adaptive frequency clock signal, Patent Number: US 6922111

- Clock signal generation and distribution via ring oscillators, Patent Number: US 6922112

- Method and apparatus for detecting on-die voltage variations, Patent Number: US 6882238

- Method and apparatus for correcting a clock duty cycle in a clock distribution network, Patent Number: US 6750689

- Automated clock alignment for testing processors in a bypass mode, Patent Number: US 6704892

- Generating a 2-phase clock using a non-50% divider circuit, Patent Number: US 6629255

- Method and apparatus for generating 2/N mode bus clock signals, Patent Number: US 5821784

- Core clock correction in a 2/N mode clocking scheme, Patent Number: US 5834956

- Method and apparatus for generating 2/N mode bus clock signals, Patent Number: US 6104219

- Method and apparatus for clock skew compensation, Patent Number: US 6192092

- Core clock correction in a 2/N mode clocking scheme, Patent Number: US 6208180

- Core clock correction in a 2/n mode clocking scheme, Patent Number: US 6268749

- Clock distribution system for selectively enabling clock signals to portions of a pipelined circuit, Patent Number: US 6611920

- Details

- Written by Javed Barkatullah

- Category: About

Barkatech Consulting, LLC is a member of EE Consult Oregon, which is the Oregon chapter of the Alliance of IEEE Consultants' Networks (AICN), a nationwide organization of electrical and electronic consultants.

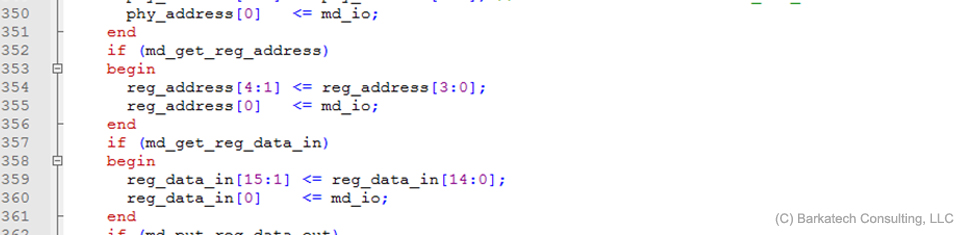

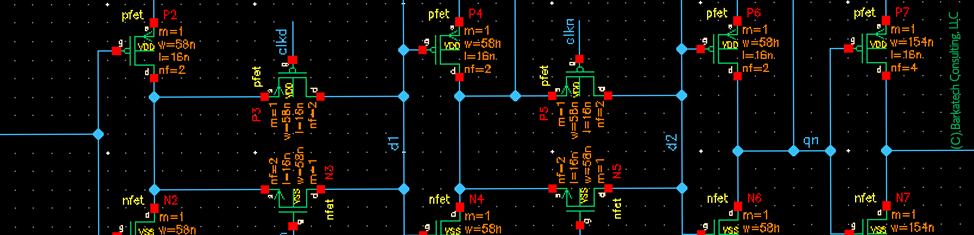

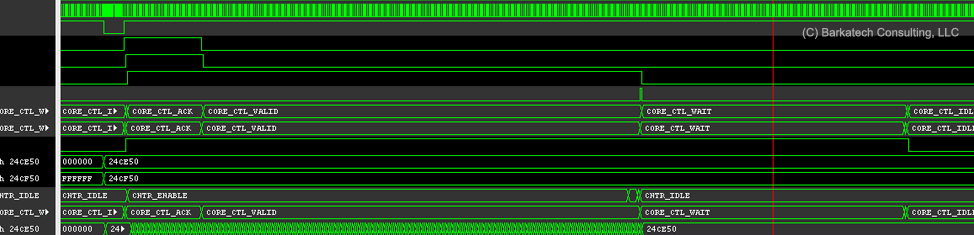

Dr. Javed Barkatullah is the Principal / Founder of Barkatech Consulting, LLC. He is a silicon design industry veteran with over 23 years of diverse research, design and management experience. Dr. Barkatullah is currently engaged as a consultant to Everspin Technologies, Inc. for the design and implementation of a new MRAM (Magnetic Random Access Memory) chip using spin-torque technology. His last project involved the research, design and implementation of high performance, power efficient custom ASICs and system for Bitcoin mining application for Cointerra, Inc. of Austin TX. Previously, he had worked on developing 2D to 3D conversion algorithms, software and hardware.

Dr. Barkatullah was a co-founder and CEO of a mobile social network marketing company, Gobenow, Inc. He designed and developed the business model, technology and apps for the mobile marketing platform. Previously, Dr. Barkatullah has served as Principal Engineer/Manager at Nvidia Corporation, member Technical Staff at Stexar Corporation, and Senior Principal Engineer at Intel Corporation. He is a visionary technologist, experienced business leader with strong interdisciplinary skills and expertise. He has expertise in research, design, implementation and verification of high performance circuits and in the management of technology projects. He has played leadership role in advanced microprocessors, video processors and graphics processors design projects.He received the Intel Achievement Award in 1996 for outstanding contributions to low power processor design.

Dr. Barkatullah received his Masters and PhD degrees in Electrical & Computer Engineering from University of Iowa, and an MBA degree from Willamette University. He also has a Certificate in Sustainable Enterprise from Willamette University. Dr. Barkatullah has over thirty patents in the field of high-speed circuit designs and has many technical publications in the IEEE journals. He has served as an associate editor of IEEE Journal of Solid State Electronics from June 2004 to October 2005.